USRP N300

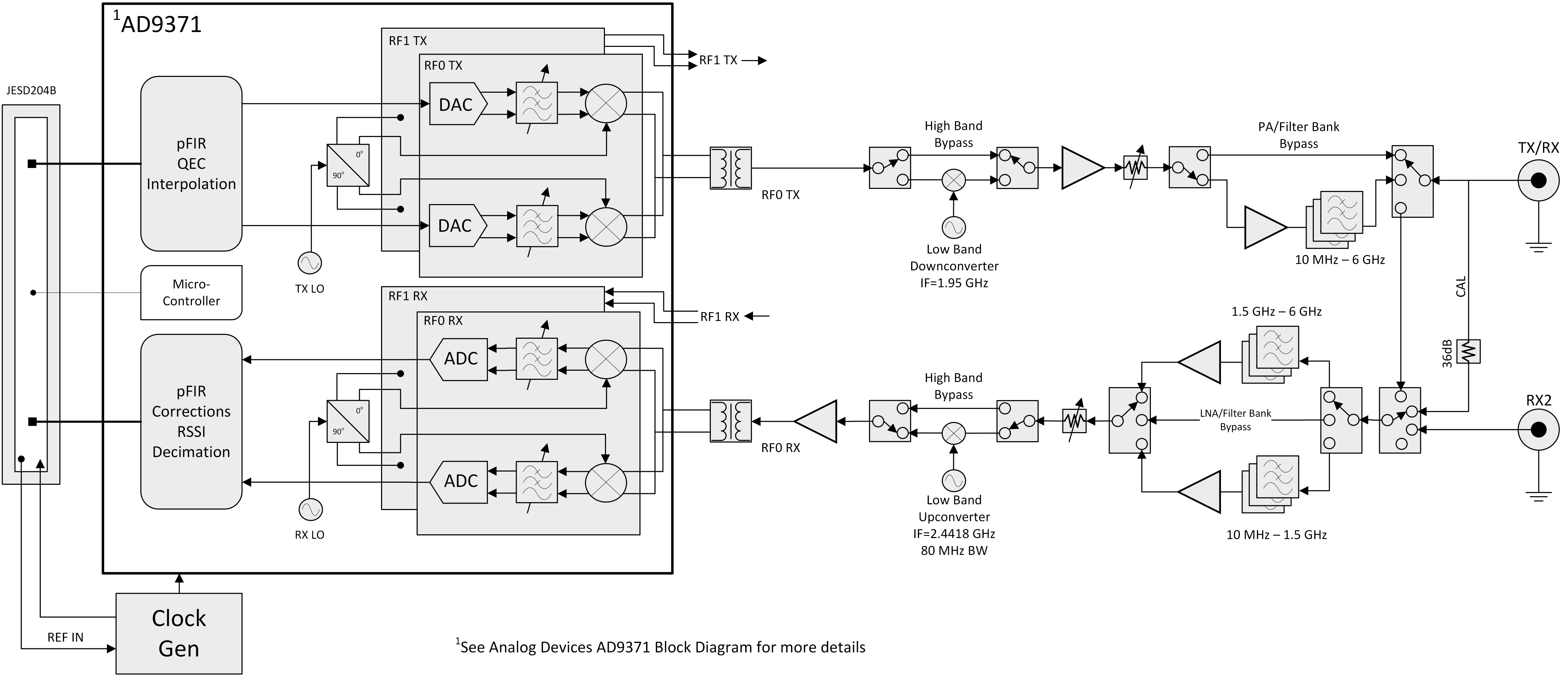

USRP N300 là một biến thể với chi phí thấp hơn của USRP N310, cung cấp độ tin cậy và khả năng chịu lỗi để triển khai trong các hệ thống không dây phân tán và quy mô lớn. USRP N300 đơn giản hóa việc kiểm soát và quản lý mạng vô tuyến bằng thực hiện từ xa các tác vụ như cập nhật phần mềm, khởi động lại, khôi phục cài đặt gốc, tự kiểm tra, gỡ lỗi máy chủ PC / ARM và theo dõi tình trạng hệ thống. Mặt trước RF sử dụng bộ thu phát AD9371, công nghệ RFIC mới nhất, để cung cấp khả năng MIMO 2X2, băng thông tức thời lên đến 100 MHz và dải tần mở rộng từ 10 MHz đến 6 GHz.

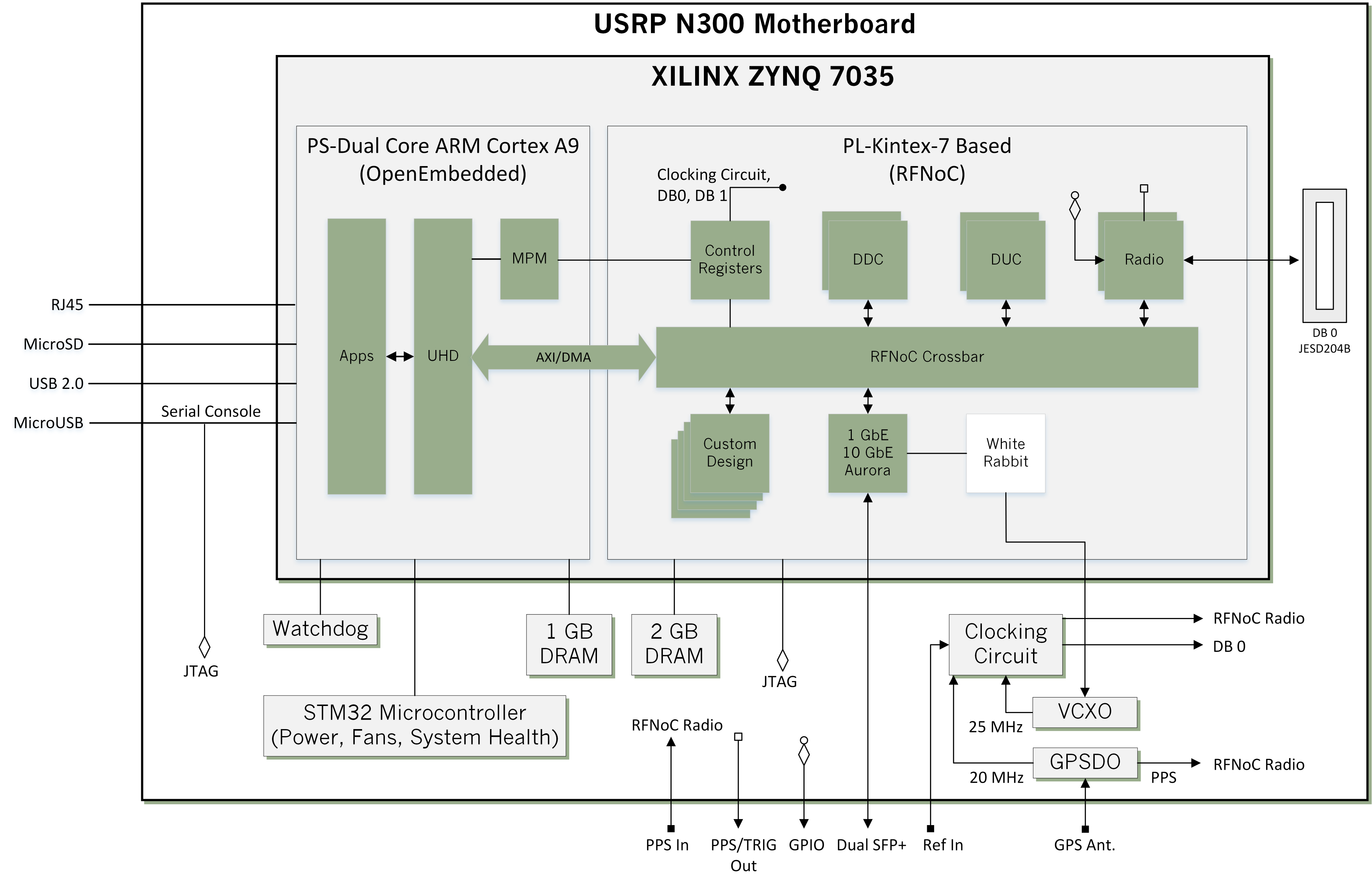

Bộ xử lý băng tần cơ sở sử dụng SoC Xilinx Zynq-7035 để cung cấp FPGA do người dùng lập trình để xử lý thời gian thực, độ trễ thấp và CPU ARM lõi kép để hoạt động độc lập. Người dùng có thể triển khai các ứng dụng trực tiếp trên hệ điều hành Linux nhúng được cài đặt sẵn hoặc truyền các mẫu tới máy tính chủ sử dụng các giao diện tốc độ cao như 1 Gigabit Ethernet, 10 Gigabit Ethernet và Aurora qua hai cổng SFP +. USRP N300 có kiến trúc đồng bộ hóa linh hoạt với hỗ trợ các phương pháp đồng bộ hóa SDR truyền thống như xung Clock tham chiếu, tham chiếu thời gian PPS và GPSDO, cho phép triển khai các hệ thống MIMO đếm kênh cao.

Tổng quan

USRP N300 đơn giản hóa việc kiểm soát và quản lý mạng vô tuyến bằng cách thực hiện từ xa các tác vụ như cập nhật phần mềm, khởi động lại, khôi phục cài đặt gốc, tự kiểm tra, gỡ lỗi máy chủ PC/ARM và theo dõi tình trạng hệ thống. Mặt trước RF sử dụng bộ thu phát AD9371, công nghệ RFIC mới nhất, để cung cấp khả năng MIMO 2X2, băng thông tức thời lên đến 100 MHz và dải tần mở rộng từ 10 MHz đến 6 GHz.

API USRP Hardware Driver (UHD) mã nguồn mở và khung phát triển RF Network-on-Chip (RFNoC) FPGA giúp ghỗ trợ phát triển phần mềm và tích hợp với nhiều công cụ tiêu chuẩn ngành như GNU Radio. Người dùng có thể nhanh chóng tạo mẫu và triển khai các thiết kế một cách đáng tin cậy cho nhiều ứng dụng SDR như máy đo không dây, đầu vô tuyến từ xa, giám sát phổ, v.v. Xin lưu ý rằng USRP N300 không được thiết kế để điều chỉnh nhanh.

Bộ xử lý băng tần cơ sở sử dụng SoC Xilinx Zynq-7035 để cung cấp FPGA do người dùng lập trình để xử lý thời gian thực , độ trễ thấp và CPU ARM lõi kép để hoạt động độc lập. Người dùng có thể triển khai các ứng dụng trực tiếp trên hệ điều hành Linux nhúng được cài đặt sẵn hoặc truyền các mẫu tới máy tính chủ sử dụng các giao diện tốc độ cao như 1 Gigabit Ethernet, 10 Gigabit Ethernet và Aurora qua hai cổng SFP +. USRP N300 có kiến trúc đồng bộ hóa linh hoạt với hỗ trợ các phương pháp đồng bộ hóa SDR truyền thống như xung Clock tham chiếu, tham chiếu thời gian PPS và GPSDO, cho phép triển khai các hệ thống MIMO đếm kênh cao.

Bộ xử lý băng tần cơ sở

Bộ xử lý băng tần cơ sở sử dụng SoC Xilinx Zynq-7035 để cung cấp FPGA do người dùng lập trình để xử lý thời gian thực, độ trễ thấp và CPU ARM lõi kép để hoạt động độc lập. Người dùng có thể triển khai các ứng dụng trực tiếp trên hệ điều hành Linux nhúng được cài đặt sẵn hoặc truyền các mẫu tới máy tính chủ sử dụng các giao diện tốc độ cao như 1 Gigabit Ethernet, 10 Gigabit Ethernet và Aurora qua hai cổng SFP+.

Đồng bộ hóa

USRP N300 có kiến trúc đồng bộ hóa linh hoạt với hỗ trợ các phương pháp đồng bộ hóa SDR truyền thống như tham chiếu xung clock, tham chiếu thời gian PPS và GPSDO, cho phép triển khai các hệ thống MIMO đếm kênh cao. Ngoài ra, USRP N300 có tính năng đồng bộ hóa dựa trên Ethernet bằng cách sử dụng giao thức định thời White Rabbit nguồn mở. White Rabbit cho phép đồng bộ hóa băng tần chính xác trong khoảng cách lớn trong môi trường mà GPS bị từ chối. Để biết thêm thông tin, hãy xem ghi chú “Đồng bộ hóa dựa thông qua Ethernet trên thiết bị USRP N3xx” trên mục Ettus Research Knowledgebase.

- Triển khai đáng tin cậy và chịu được lỗi

- Khả năng quản lý từ xa

- Hoạt động độc lập (nhúng) hoặc dựa trên máy chủ (phát trực tuyến mạng)

- Được tích hợp và lắp ráp hoàn chỉnh (USRP N300 không hỗ trợ daughtercard có thể hoán đổi)

- Dải tần số mở rộng 10 MHz đến 6 GHz

- Lên đến 100 MHz băng thông tức thời trên mỗi kênh

- 2 RX, 2TX trong hệ số dạng RU nửa rộng [1]

- Dải bộ lọc RX, TX

- ADC 16 bit, DAC 14 bit

- Tốc độ mẫu có thể định nghĩa: 122,88, 125 và 153,6 MS / s

- Xilinx Zynq-7035 SoC

- CPU lõi kép ARM Cortex-A9 800 MHz

- Hai cổng SFP + (1 Gigabit Ethernet, 10 Gigabit Ethernet, Aurora)

- RJ45 (1 GbE) [2]

- Tham chiếu xung clock

- Tham chiếu thời gian PPS

- GPSDO tích hợp

- Đồng bộ hóa thôn qua Ethernet sử dụng giao thức White Rabbit

- 1 cổng máy chủ USB Loại A

- 1 cổng micro-USB (bảng điều khiển nối tiếp, JTAG)

- Bộ đếm thời gian Watchdog

- Chứng nhận CE

- OpenEmbedded Linux

- API phần mềm nguồn mở USRP Hardware Driver ™ (UHD) phiên bản 3.11.0.1 trở lên

- Khung phát triển mạng RF trên chip (RFNoC ™) FPGA

- Xilinx Vivado 2017.4 Design Suite (không bao gồm giấy phép)

- Hỗ trợ GNU Radio được duy trì bởi Ettus Research™ thông qua GR-UHD, một giao diện với UHD được phân phối bởi GNU Radio

[1] Mặt trước RF sử dụng bộ thu phát AD9371 có thể điều chỉnh độc lập. Bộ thu phát có khả năng hoạt động MIMO 2X2.

[2] Cổng RJ45 được sử dụng để quản lý thiết bị từ xa và không hỗ trợ phát trực tuyến IQ.

Các thành phần trong hộp

- Thiết bị USRP N300

- Cáp Ethernet RJ45

- Bộ chuyển đổi SFP + sang RJ45

- Thẻ nhớ microSD

- Nguồn cấp