FPGA guide

Develop an FPGA VI

Develop your own FPGA-targeted VI to take advantage of the unique capabilities of the FPGA target such as high-speed I/O, precision I/O timing, parallel processing, and functionality not offered by the RT processor and Academic RIO Device Toolkit default personality; you can also augment the default personality with your needed capability.

Summary

- Develop an FPGA VI when you need a capability that does not exist in the Academic RIO Device Toolkit and default FPGA personality:

- Create your own FPGA personality when you have no need of any of the functionality provided by the Academic RIO Device Toolkit, e.g., Express VIs for digital I/O, analog I/O, SPI and I2C communication, etc., or

- Modify the default Device FPGA personality to add your own functionality while retaining some or all of the existing functionality

- Compiling (building) the FPGA bitfile is a relatively long process (at least 5 minutes or so), therefore use simulation techniques to debug your code before committing to a build

Application example

This audio streaming and real-time processing application example illustrates how to create a custom FPGA VI that samples the Academic RIO Device stereo audio input, sends blocks of samples (“audio frames”) to the RT for processing, and plays the processed audio frames on the Device audio output. The FPGA sampling rate defaults to 50-kHZ but can go considerably higher, thanks to the high-speed processing offered by the FPGA target.

Use cases

- Interfacing to equipment that does not use a standard data comm protocol such as I2C, SPI, and UART and which has specific timing and handshaking requirements that would be difficult or impossible to implement with the RT VI, e.g., VGA display, IR remote control for television, and MIDI ports (baud rate not supported by UART Express VI)

- Execute an algorithm faster than what is possible on the RT VI, e.g., real-time data acquisition and signal processing, and massive parallelism

- Off-load computational effort from the RT target; manage low-level details to simplify the RT VI design

- Obtain cycle-accurate jitter-free timing with 25-ns clock period (40MHz clock); derived clock domains provide shorter or longer clock periods, i.e., it is possible for some process loops to operate at even higher clock frequencies

Considerations

- Restricted palette of built-in functions and limitations on supported data types

- Completely custom bitfile eliminates use of any of the Academic RIO Device toolkit Express VIs, however, it is possible to edit the default personality to keep the necessary functionality while adding your own

- Compilation requires a minimum of 5 minutes and potentially could take hours depending on the complexity and size of the design

- Simulating the design (aka “testbenching”) is crucial for this design flow

Design flow procedure

- Create a new FPGA project to design an FPGA from scratch, or create a new project to modify the default Academic RIO Device FPGA personality

- Design the FPGA VI architecture using one or more of these coding styles:

- Similar to the way you would create a VI for the PC or RT,

- “Think like hardware” with gates, registers, counters, state machines, and register-level transfer (RTL) design techniques; see the external resource Digital Circuits and Systems with LabVIEW FPGA for a full treatment of how to use design methods for digital logic and systems in the LabVIEW environment,

- Import existing VHDL code, or

- Use configurable Xilinx IP (intellectual property) blocks.

- Use derived clock domains to operate portions of the VI code at lower or higher clock frequencies than the default 40-MHz clock

- Communicate between parallel processing loops using global and local variables

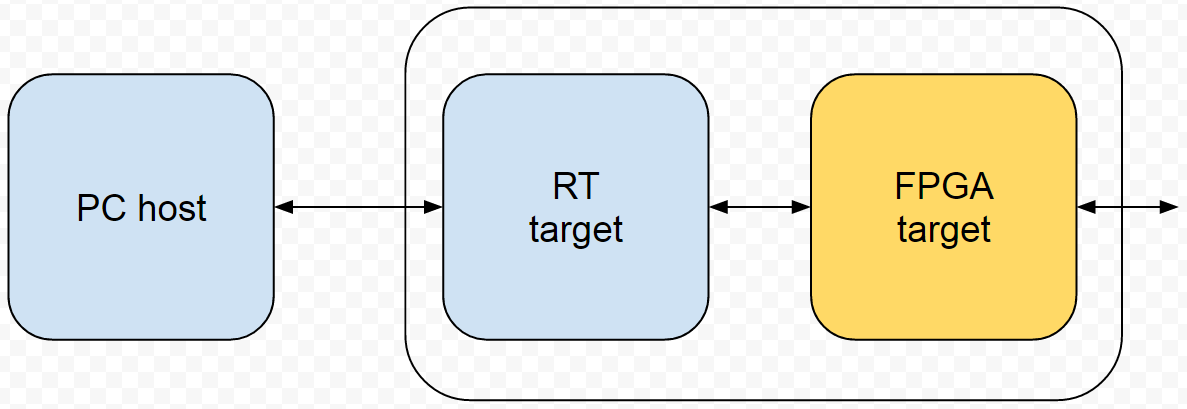

- Exchange data or messages with the RT or PC using inter-target communication techniques

- Simulate the VI and thoroughly debug it to ensure correct functionality before you expend effort compiling the VI

- Debugging techniques include execution highlighting, breakpoints, and probes

- Sampling probes provide familiar waveform-based views of activity

- A PC VI can be developed to interact with the simulated FPGA model as a more sophisticated way to exercise the FPGA VI inputs and to observe the resulting outputs

- Compile the FPGA VI to a bitfile using your own computer or a cloud-based compiler; compiling in the cloud may take a little longer, but it removes the burden from your own machine and permits multiple FPGA VIs to be compiled at once

For more information

- FPGA Fundamentals (http://www.ni.com/white-paper/6983/en)

General introduction to field-programmable gate arrays (FPGAs) and their role in the NI RIO technology platform

- NI LabVIEW High-Performance FPGA Developer's Guide (http://www.ni.com/tutorial/14600/en)

A thoroughly useful resource, available as a PDF download. Detailed discussion of the single-cycle timed loop (SCTL) and how it differs from the conventional while-loop structure.

- NI LabVIEW for CompactRIO Developer's Guide (http://www.ni.com/compactriodevguide/)

A thoroughly useful resource, available as a PDF download. Includes sample code.