Site map: Code examples

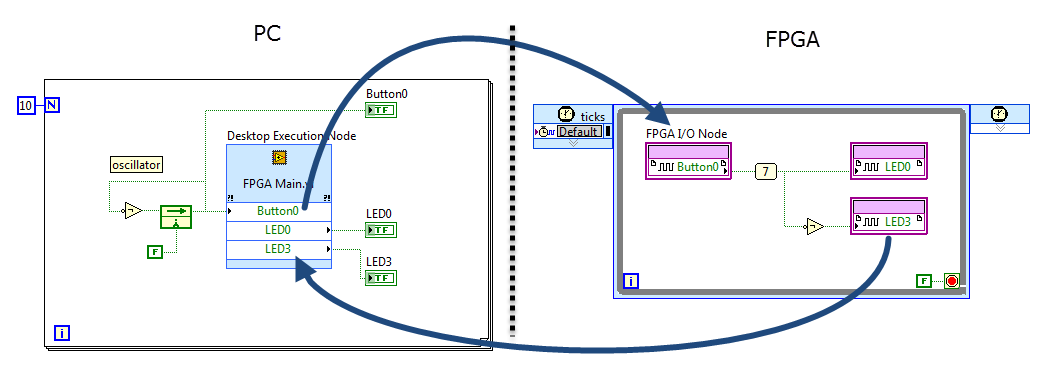

"Desktop Execution" node as an FPGA VI testbench

FPGA code PC code

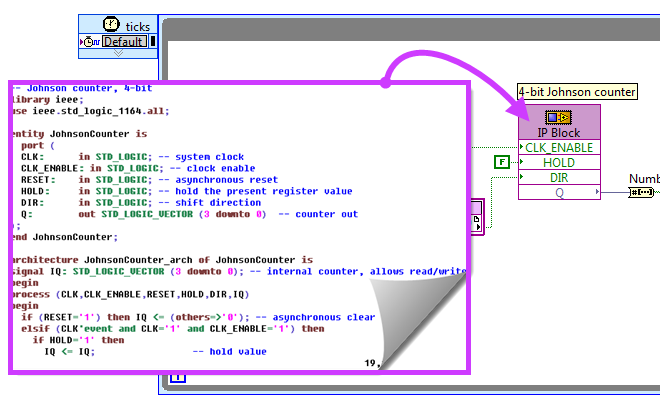

Derived clock domains

FPGA code

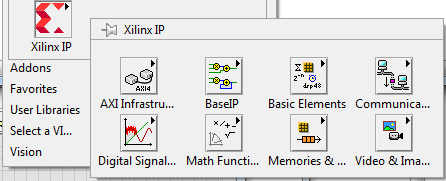

Xilinx IP integration

FPGA code

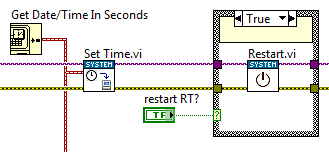

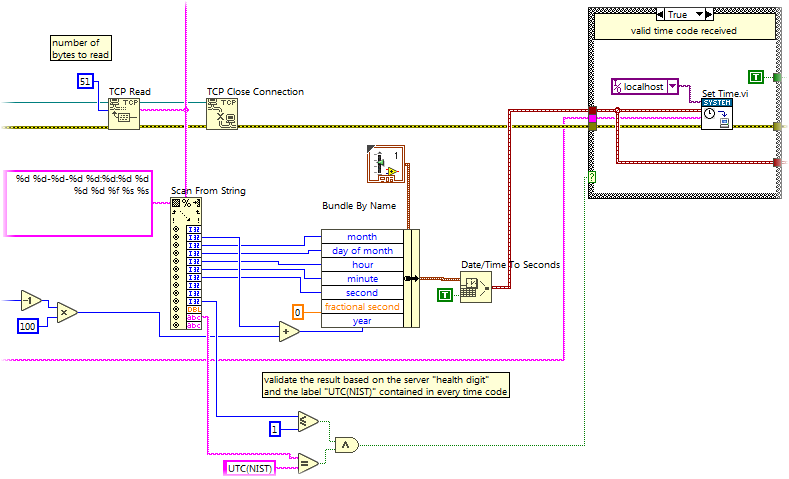

Set RT system time/date from PC

RT code PC code

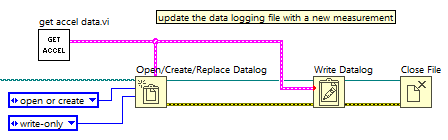

Headless datalogger and file I/O

RT code

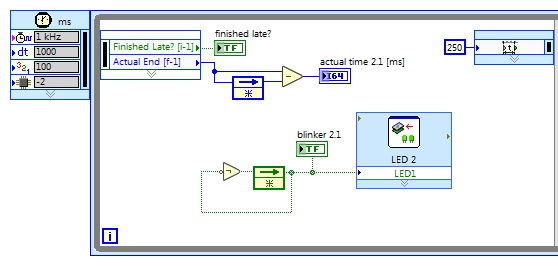

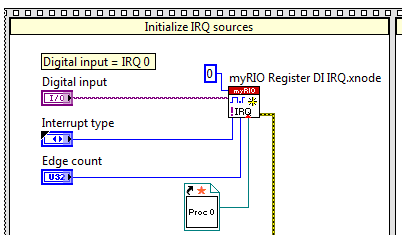

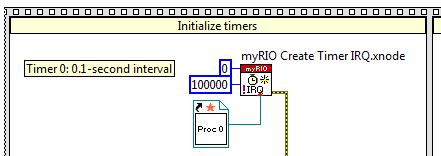

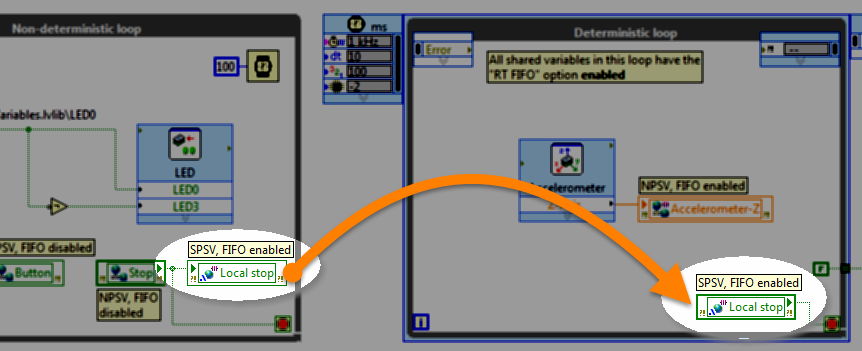

Timed loop

RT code

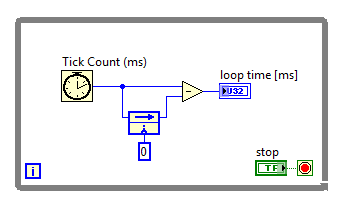

Measure loop iteration time

RT code

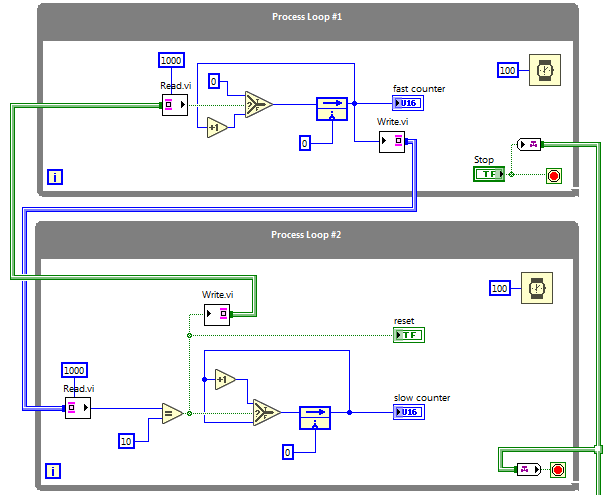

Local variable (RT)

RT code

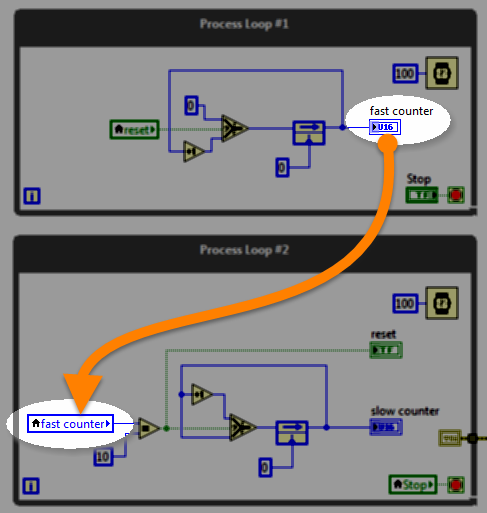

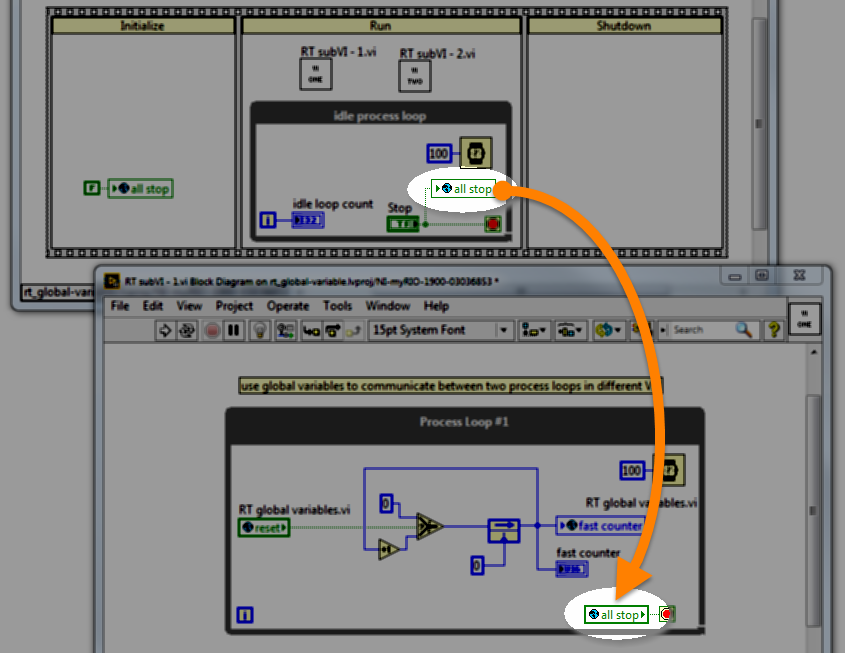

Global variable (RT)

RT code

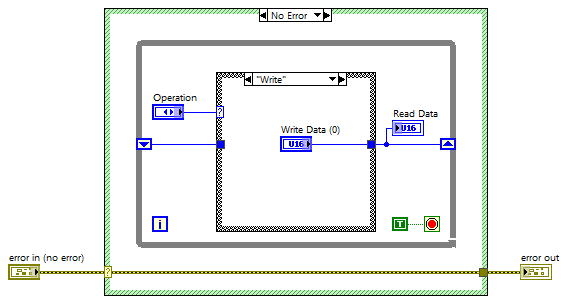

Functional global variable (FGV)

RT code

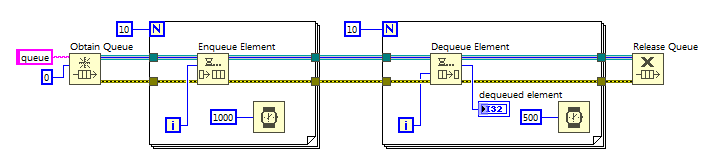

Queue

RT code

Channel wire

RT code

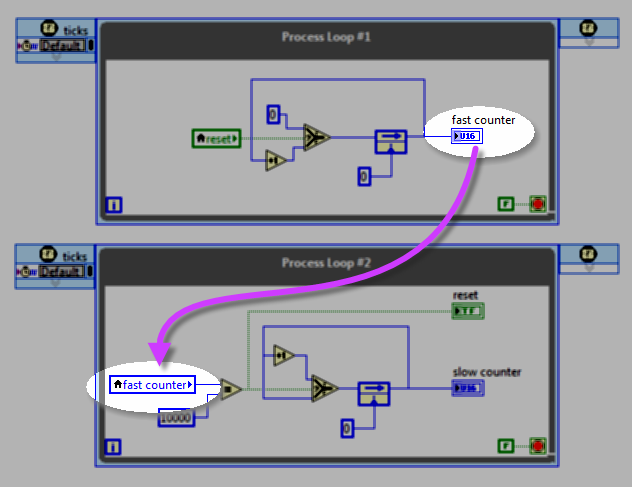

Local variable (FPGA)

FPGA code

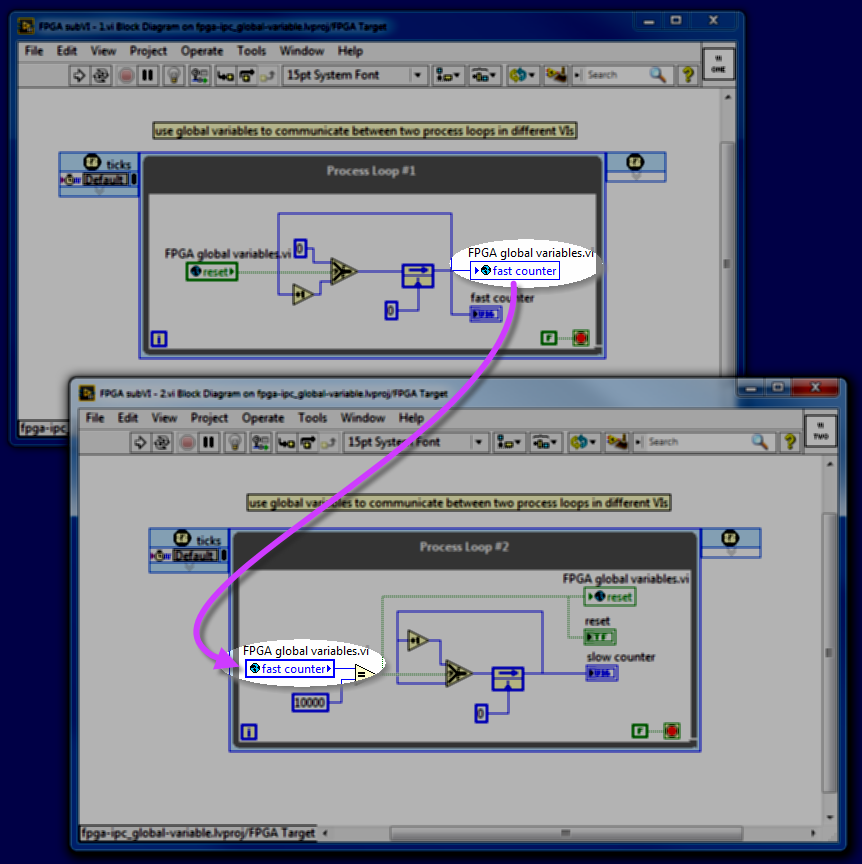

Global variable (FPGA)

FPGA code

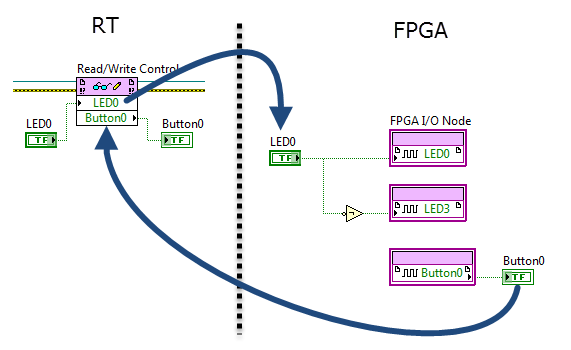

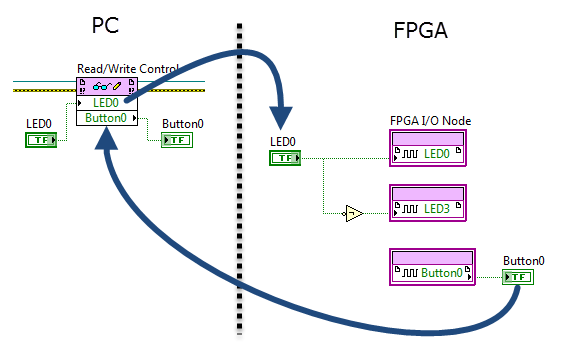

Programmatic front-panel communication with RT

FPGA code RT code

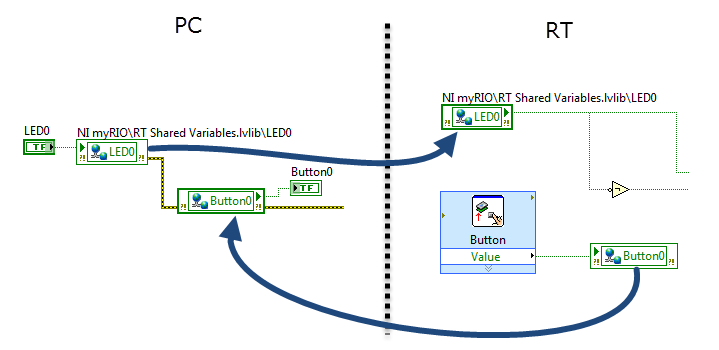

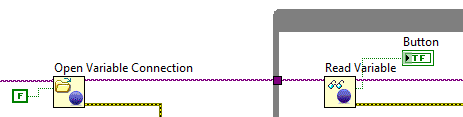

Network-published shared variable (NPSV)

RT code PC code

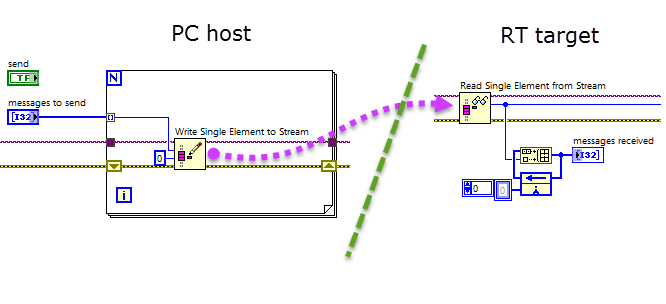

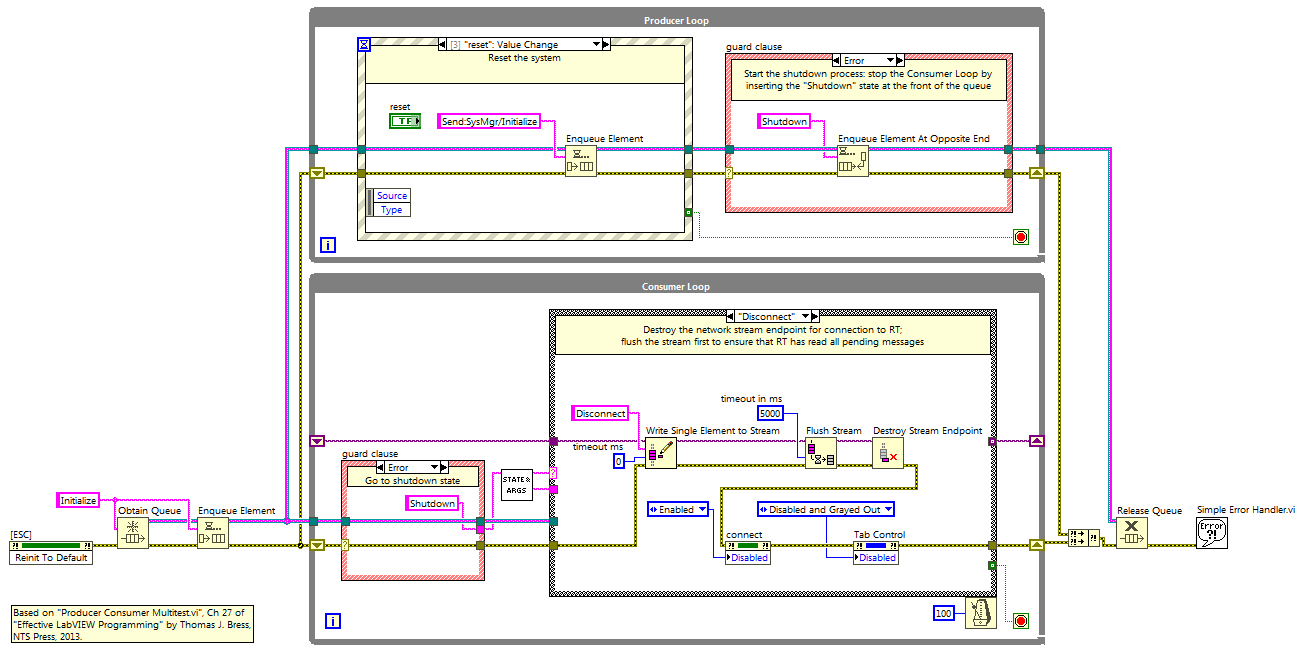

Send messages through a network stream channel

RT code PC code

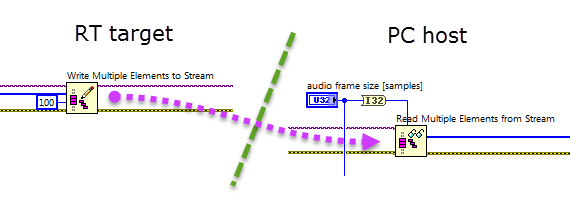

Stream high-speed data through a network stream channel

RT code PC code

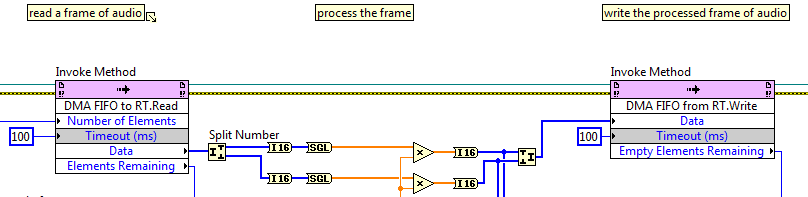

Stream high-speed data between FPGA and RT with a DMA FIFO

FPGA code RT code

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

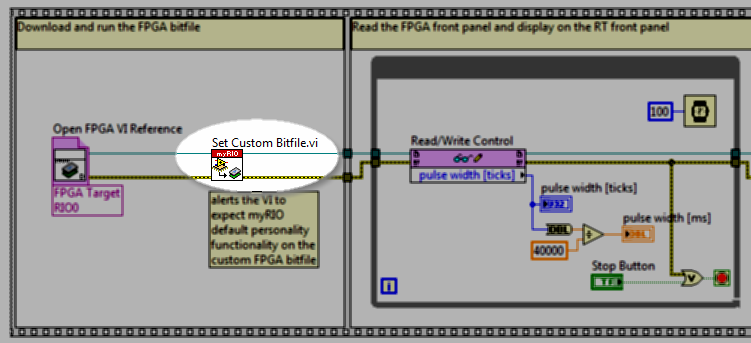

Programmatic front-panel communication with PC

FPGA code PC code

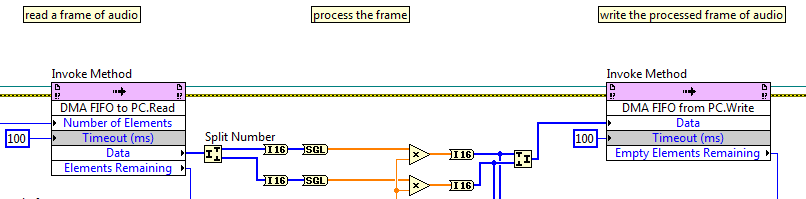

Stream high-speed data between FPGA and PC with a DMA FIFO

FPGA code PC code

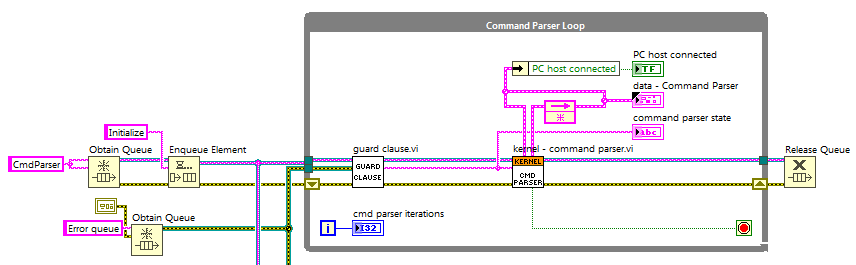

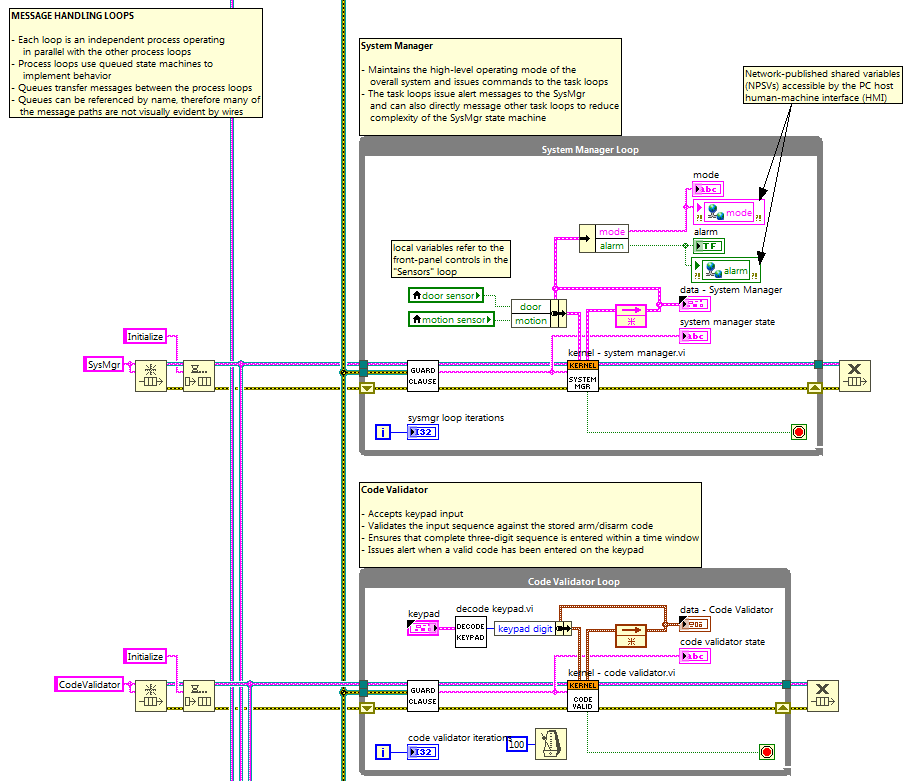

Queued state machine

RT code

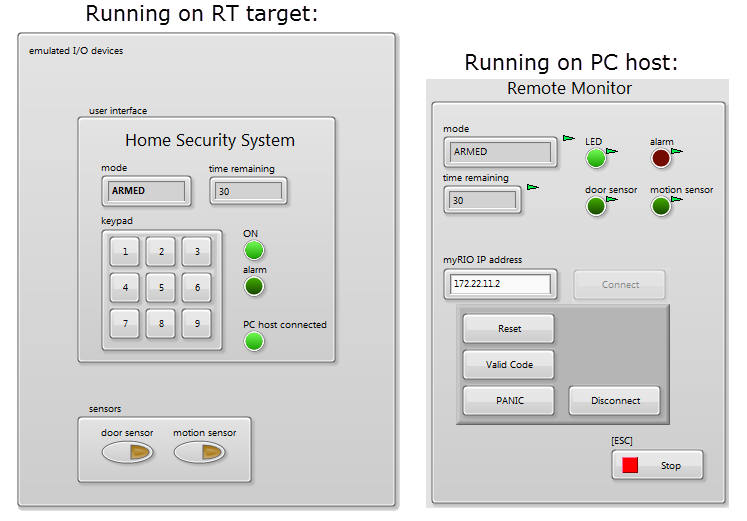

System controller application example: Home Security System

RT code PC code

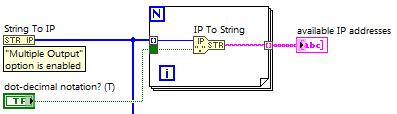

Show available IP addresses

RT code PC code

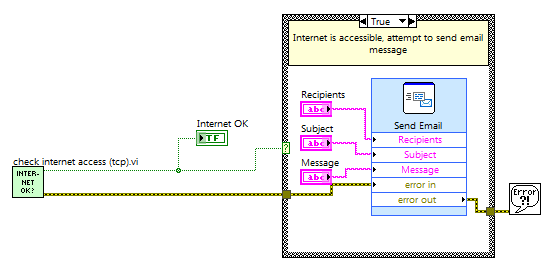

Send an email or text message

RT code

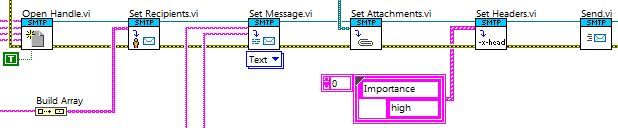

Send a file as an email attachment with high priority (remote webcam photo logger application)

RT code

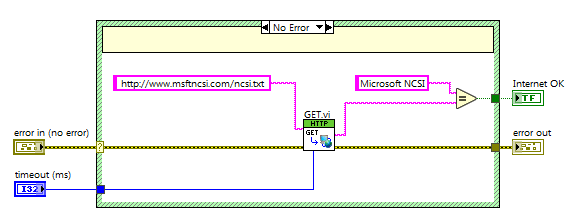

Check Internet access (HTTP method)

RT code PC code

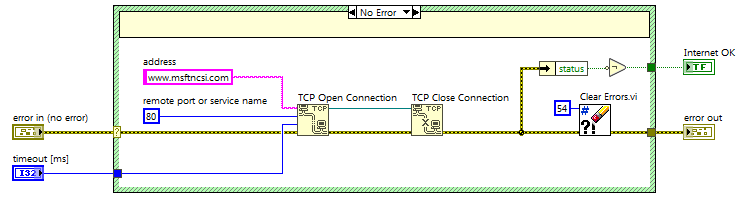

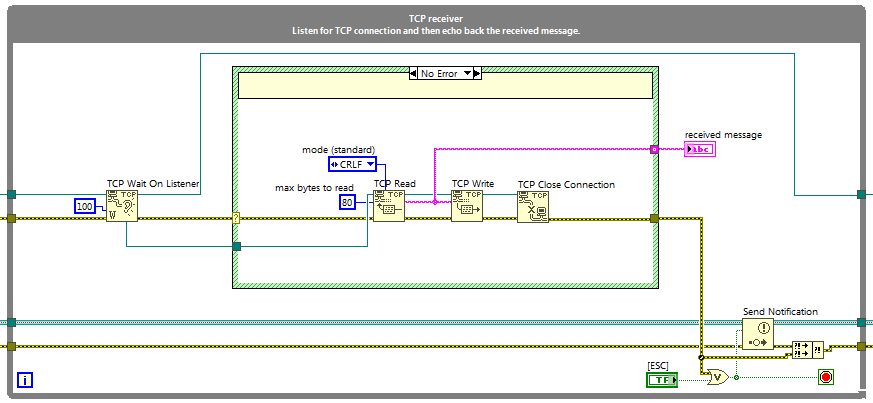

Check Internet access (TCP method)

RT code PC code

TCP/IP sender and receiver and "TCP ping" application

RT code PC code

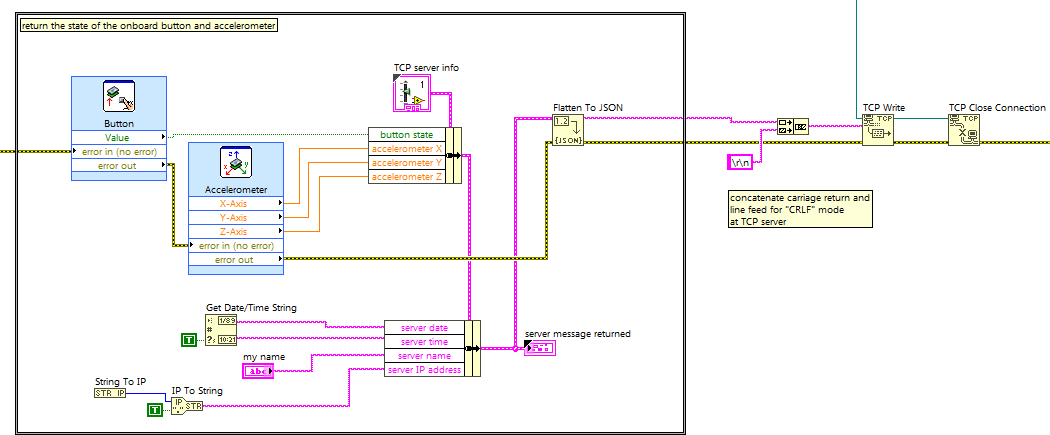

TCP client-server

RT code PC code

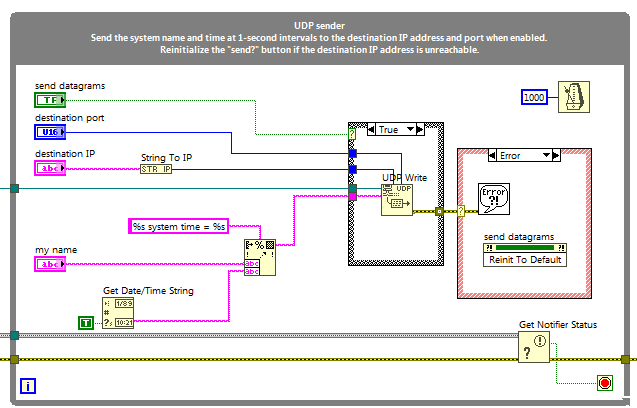

UDP sender and receiver and "UDP ping" application

RT code PC code

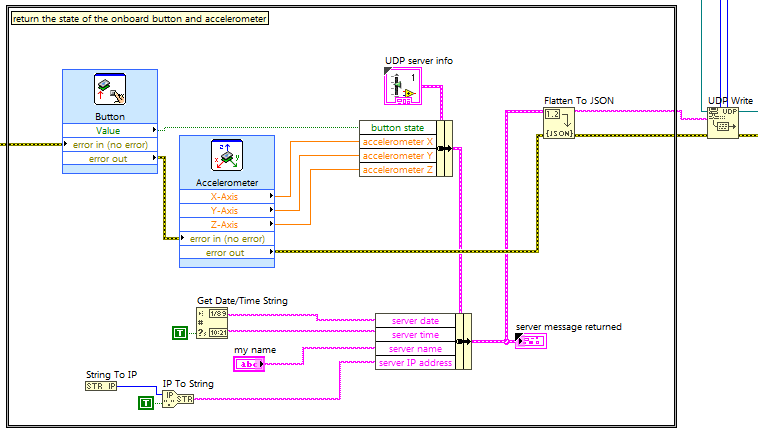

UDP client-server

RT code PC code

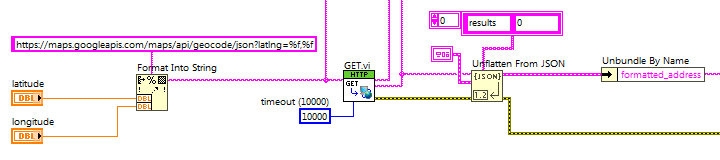

Call a Web service

RT code

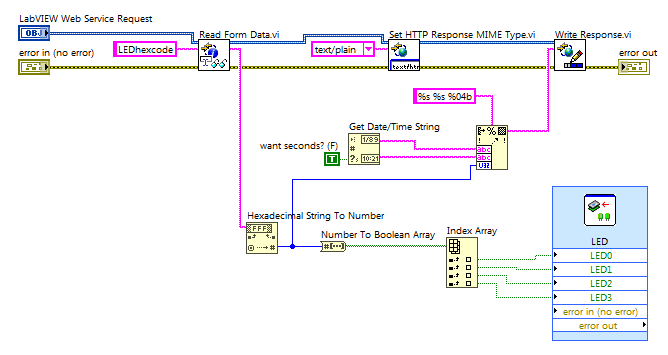

Host a Web service

RT code