RIO Developer Essentials Guide for Academia

FPGA code example

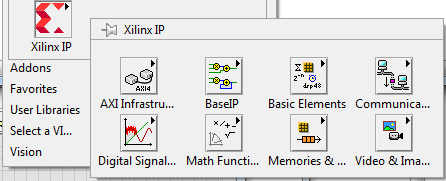

Xilinx IP integration

Configure and use Xilinx IP (intellectual property) modules designed specifically for the Xilinx Zynq FPGA

Use cases

- Use configurable Xilinx IP modules to efficiently implement counters, registers, block RAM, math and DSP functions, serial communications (SPI, I2C), and video and image processing

Features

- IP modules are fully configurable

- Fully supported by the LabVIEW FPGA simulation environment

Keep in mind

- Any change in a configured IP block necessitates a full recompile of the entire VI

LabVIEW block diagram elements

Locate these elements with "Quick Drop" (press Ctrl+Space and start typing the name); click on an icon to see more sample code that uses that element:Example code

- Connect your Academic RIO Device to your PC using USBLAN, Ethernet, or Wi-Fi. NOTE: Not all Academic RIO Devices have Ethernet and Wi-Fi connectivity options.

-

Download and unpack the

fpga_xilinx-ip.zip (for use with NI myRIO 1900)

or the

NIELVISIII-fpga_xilinx-ip.zip (for use with NI ELVIS III)

archive, and then double-click the ".lvproj" file to open the project. NOTE: This project was written for a NI myRIO 1900 or NI ELVIS III connected by USBLAN at IP address 172.22.11.2.

If you are using a different IP address or another Academic RIO Device (Example: NI myRIO 1950 or NI RIO Control Module) do the following:

- If using the NI myRIO 1950 or NI RIO Control Module start with the NI myRIO 1900 Archive.

- Different IP address: Right-click on the "NI myRIO 1900" Device, choose "Properties", and then enter the new IP address

- Different device:

- Right-click on the top of the project hierarchy, select "New Targets and Devices", keep the "Existing target or device" option, and then find and select your particular device

- Select all of the components under the "NI myRIO 1900" device: click the first one and then shift+click the last one

- Drag the selected components to the new device

- Right-click the "NI myRIO 1900" device and select "Remove from project"

- Run the “FPGA Main” VI and observe the Academic RIO Device onboard LEDs for the 4-bit up-counter pattern: 0000, 0001, 0010, 0100, 0101, etc.

- Stop the VI by clicking the “Abort” button.

Expected results

https://youtu.be/VIW5z_Dn1QA (0:39)

Developer walk-through

https://youtu.be/E2-aMAt1Cm8 (3:48)

Outline

- Review overall structure

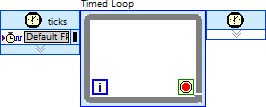

- One single-cycle timed loop (SCTL) contains all logic and I/O (onboardLEDs); conditional terminal wired to “False” constant as is typical for FPGA VIs

- Binary counter from Xilinx IP library generates clock enable pulse

- Second binary counter from Xilinx IP library implements 4-bit counter

- Browser other Xilinx IP library elements, some quite sophisticated

- Configure the Xilinx IP binary counter: clock-enable pulse

- Select output width = 25 and increment value = 1

- Select final count value as 20,000,000 (0x1312D00) to obtain an enable pulse once every 0.5 seconds with 40 MHz system clock

- Compare resource estimates for “Fabric” or “DSP48” implementation

- Select Count Mode = UP

- Enable synchronous threshold output with threshold value = 1

- Ignore clock enable and reset signals for this basic counter

- Confirm I/O ports are assigned correctly

- Configure the Xilinx IP binary counter: 4-bit up-counter

- Select output width = 4 and increment value = 1

- Compare resource estimates for “Fabric” or “DSP48” implementation

- Select Count Mode = UP

- Enable “Clock Enable” input

- Confirm I/O ports are assigned correctly

For more information

Integrating Third-Party IP (FPGA Module) (https://zone.ni.com/reference/en-XX/help/371599K-01/lvfpgaconcepts/integrating_hdl/)Additional details regarding how VHDL and other source types may be imported into the block diagram.