RIO Developer Essentials Guide for Academia

RT code example

Headless datalogger and file I/O

Monitor process variables and sensor measurements, timestamp them, and log them to a file, and then remote access the datalog file through the network with WebDAV, web browser, or VI running on a PC host.

Use cases

- Long-term sensor monitoring in a remote location

- Time-stamped data logging to a network-accessible datalog file

Features

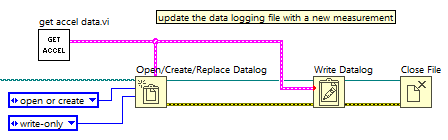

- Create, update, and read data logging files with the convenient LabVIEW “Datalog” VIs

- Define your datalog record format with a user-defined cluster control

- Access the network-accessible datalog file with any or all of these methods:

- Browse directly to the Academic RIO Device network address, e.g., http://172.22.11.2/files when the Device is connected by the USB cable – this is a quick way to view or save the datalog file

- Use the WebDAVWeb Distributed Authoring and Versioning, an Internet standard mechanism for editing and managing files between remote systems. client to mount the Academic RIO Device file system as a network drive on your PC host – use this method when you need read/write access to the datalog file

- Run an HMI (human-machine interface) VI on the PC host to read the datalog file when the Device file system is mounted as a network drive

- Control the datalogger application by editing the remote configuration file either manually or through the HMI

Keep in mind

- Greatly expand the data storage capability of your datalogging application with a USB thumb drive attached to the Academic RIO Device USB port

- Access the USB thumb drive as folder “/u” on the Device file system

- The datalog file is a “binary” file defined by the cluster wired to the “Open/Create/Replace Datalog” VI – this is a space-efficient format, but not a “human readable” format like a text file; create a VI on the PC host to read the datalalog file

- Your application might require time-stamping to work properly over a long time period; if so, be aware of the following:

- The Device does not include an onboard real-time clock (RTC), therefore its system date resets to the same date on each power cycle

- In the event of an unexpected power cycle the Device automatically restarts your application if it has been deployed as the startup application, however, the system date reverts back to the original power-on system date

- You can adjust the power-on system date with NI MAX or a browser, but this does not solve the system date reversion problem

- Consider the inexpensive Digilent I2C battery-backed RTC module to preserve the true calendar date across power cycles

LabVIEW block diagram elements

Locate these elements with "Quick Drop" (press Ctrl+Space and start typing the name); click on an icon to see more sample code that uses that element:Example code

- Install the Academic RIO Device software set add-on called “WebDAV Client with SSL Support” to enable the Device file system to be mapped as a network drive on the PC host; the HMI (human-machine interface) that runs on the PC requires this drive mapping to be established

- Connect your Academic RIO Device to your PC using USBLAN, Ethernet, or Wi-Fi. NOTE: Not all Academic RIO Devices have Ethernet and Wi-Fi connectivity options.

- Connect a USB thumb drive to the Device

- Mount the Academic RIO Device file system as a network drive, e.g., as drive “R:” for “RIO”

-

Download and unpack the

rt_headless-datalogger.zip (for use with NI myRIO 1900)

or the

NIELVISIII-rt_headless-datalogger.zip (for use with NI ELVIS III)

archive, and then double-click the ".lvproj" file to open the project. NOTE: This project was written for a NI myRIO 1900 or NI ELVIS III connected by USBLAN at IP address 172.22.11.2.

If you are using a different IP address or another Academic RIO Device (Example: NI myRIO 1950 or NI RIO Control Module) do the following:

- If using the NI myRIO 1950 or NI RIO Control Module start with the NI myRIO 1900 Archive.

- Different IP address: Right-click on the "NI myRIO 1900" Device, choose "Properties", and then enter the new IP address

- Different device:

- Right-click on the top of the project hierarchy, select "New Targets and Devices", keep the "Existing target or device" option, and then find and select your particular device

- Select all of the components under the "NI myRIO 1900" device: click the first one and then shift+click the last one

- Drag the selected components to the new device

- Right-click the "NI myRIO 1900" device and select "Remove from project"

- Open “PC Main” and check the following:

- The “myRIO mapped drive on PC” control defaults to “R:\u”; replace the “R” with your selected network drive letter, if necessary; “\u” is the USB drive folder

- “testing.dat” is the default datalog file name; adjust this name as needed

- “data_logger_config.txt” contains three values to control the datalogger application running on the Device; “PC Main” updates this text file on each run, and you can also manually edit this file:

- Value #1: Run mode (0 => pause data collection, 1 => collect data)

- Value #2: Data logging time interval in minutes

- Value #3: Name of the datalog file

- “logging interval” defaults to 0.1 minutes; adjust as needed, although be aware that the Device data logger only checks the configuration file once during each data acquisition cycle

- Run “PC Main” to create the configuration file (ignore the “File not found” error for now… it simply indicates that the RT datalogger has not yet generated its data file)

- Open a Windows Explorer window (Windows button + E) and confirm that the “data_logger_config.txt” file has been created; double-click the .txt file and confirm that it contains the string “1 0.100000 testing.dat”, i.e., the three values described above

- Open and run “RT Main” and check the following:

- “testing.dat” now exists (refresh the Windows Explorer window)

- LED0 blinks to indicate that the datalogger application is running

- LED1 is active (indicates run mode)

- Run “PC Main” again and observe the following:

- The “# of records found” indicator should be non-zero

- All three accelerometer axes are plotted

- Change the physical orientation of the Device to see the accelerometer data change

- OPTIONAL: Ambient Light Sensor

- You may already have the Digilent PmodALS ambient light sensor on hand

- See the wiring diagram and full description in the “NI Project Essentials Guide”

- Run the “RT - Ambient light sensor tester” VI to confirm proper operation

- Edit “RT Main” according to the instructions on the block diagram to use the ALS subVI to collect data

- Run the “PC Main - ambient light sensor” VI as the HMI

Troubleshooting tips

- Browser-based access to the file system, e.g., browsing to http://172.22.11.2/files/u/, is not available when the file system is mounted as a network drive; right-click on the network drive and select “Disconnect”, if necessary

Expected results

https://youtu.be/atm2R6dXdGA (3:31)

Developer walk-through

https://youtu.be/WeH5lbnbsbk (5:04)

Outline

- Review overall structure:

- PC Main

- HMI (human-machine interface) for the datalogger running on RT target

- Writes commands to the “data_logger_config.txt” text file located on the RT target’s USB thumb drive via WebDAV remote file access through the network connection

- Reads the datalog file and plots the time history of the accelerometer

- RT Main

- No front panel controls nor indicators, i.e., “headless”

- Reads commands from the “data_logger_config.txt” text file written by PC host to control whether and how often to log data

- Blinks LED0 to indicate that the application is running

- LabVIEW project

- “get accel data” VI - returns on-board accelerometer values

- “acccel_xyz” custom control - defines a cluster of accelerometer values and timestamp

- PC Main

- PC HMI

- Runs once and stops (no looping)

- Creates datalogger configuration file from front-panel controls:

- run/pause mode (0 means pause, not zero means run)

- logging interval in minutes (can be a fraction of a minute)

- datalog file name

- Opens the datalog file

- Determines the number of records in the datalog file

- Reads all of the datalog records from the beginning of the file

- Plots the data contained in the datalog: three-axis accelerometer readings as a function of the system timestamp for each set of readings

- Closes the datalog file

- RT datalogger process loop

- Read run mode, logging interval, and datalog file name

- Indicate run mode on LED1

- Run mode:

- 0: Wait for five seconds

- 1 (or not 0): run “get accel data” VI to obtain the three accelerometer axis values and system timestamp as a cluster, open the datalog file, write the cluster as a datalog record, and close the datalog file

- Wait for the logging interval (number of minutes specified by PC host)

- Loop runs indefinitely

- Locate the functions subpalette

- File I/O functions:

- “Path Constant”

- “Build Path”

- “Format Into File”

- “Scan From File”

- “Close File”

- Datalogger functions:

- “Open/Create/Replace Datalog”

- “Get Number of Records”

- “Set Datalog Position”

- “Read Datalog”

- “Write Datalog”

- File I/O functions: