RIO Developer Essentials Guide for Academia

FPGA code example

Global variable (FPGA)

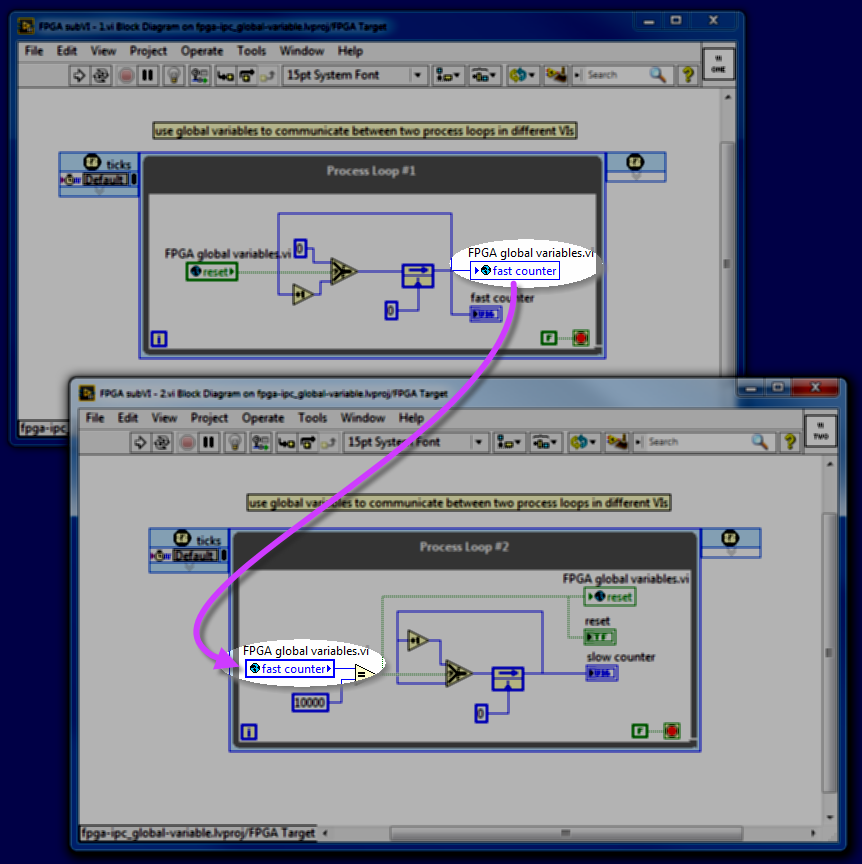

Use a global variable to communicate between two parallel process loops contained within different VIs under the same target.

Use cases

- Communicate data, control, and status between two or more parallel process loops contained within the same target (“target-scoped”) and possibly in different VIs

- Make the latest value of a variable available to other process loops

Features

- Stores values in global variables

- Tag-based (latest value) communication

- Easy to code

- Supports multiple clock domains:

- Single-cycle timed loops (SCTLs) with derived clock domains

- SCTLs and conventional while-loop structures

Keep in mind

- Because this is tag-based (latest value) communication, rapid changes of a variable in one process can be missed in the other process

- Ensure that control signals remain active long enough for the other process to detect them, or devise a hand-shaking scheme

- Conventional while-loop structures require at least two clock cycles per iteration

- Consider local variables if you only need to communicate between process loops in the same VI

LabVIEW block diagram elements

Locate these elements with "Quick Drop" (press Ctrl+Space and start typing the name); click on an icon to see more sample code that uses that element:Example code

- Connect your Academic RIO Device to your PC using USBLAN, Ethernet, or Wi-Fi. NOTE: Not all Academic RIO Devices have Ethernet and Wi-Fi connectivity options.

-

Download and unpack the

fpga_global-variable.zip (for use with NI myRIO 1900)

or the

NIELVISIII-fpga_global-variable.zip (for use with NI ELVIS III)

archive, and then double-click the ".lvproj" file to open the project. NOTE: This project was written for a NI myRIO 1900 or NI ELVIS III connected by USBLAN at IP address 172.22.11.2.

If you are using a different IP address or another Academic RIO Device (Example: NI myRIO 1950 or NI RIO Control Module) do the following:

- If using the NI myRIO 1950 or NI RIO Control Module start with the NI myRIO 1900 Archive.

- Different IP address: Right-click on the "NI myRIO 1900" Device, choose "Properties", and then enter the new IP address

- Different device:

- Right-click on the top of the project hierarchy, select "New Targets and Devices", keep the "Existing target or device" option, and then find and select your particular device

- Select all of the components under the "NI myRIO 1900" device: click the first one and then shift+click the last one

- Drag the selected components to the new device

- Right-click the "NI myRIO 1900" device and select "Remove from project"

- Run the “FPGA Main” VI in simulation mode

- Open the front panels of the two VIs contained in “FPGA Main” by double-clicking their icons in the block diagram:

- The “fast counter” in Process Loop #1 of “VI one” increments once each clock cycle

- The Boolean “reset” generated by Process Loop #2 of “VI two” resets the fast counter

- The “slow counter” in Process Loop #2 increments each time the fast counter reaches 10,000 counts; this condition also enables the “reset” signal

- Stop the VI by clicking the “Abort” button

Expected results

https://youtu.be/9hHIHq8JG9E (1:11)

Developer walk-through

https://youtu.be/3YLmRBs_bKE (3:33)

Outline

- Review overall structure:

- RT Main

- Run two VIs

- Runs forever; stop with “Abort” button

- RT subVI-1: “fast counter”

- Displays up-counter value as front-panel indicator

- Writes counter value to global variable “fast counter”

- Resets counter to zero when global variable “reset” is true

- RT subVI-2: “slow counter”

- Displays up-counter displayed as front-panel indicator

- Increments counter when the “fast counter” global variable equals 10,000

- Activates “reset” indicator and corresponding global variable when the “fast counter” value equals 10,000

- RT Main

- Create a global variable from scratch

- A special VI without a block diagram

- Place a new global variable

- Double-click it to open

- Add indicators and controls as needed

- Save the VI

- Select the desired variable

- Update an existing global variable VI

- Double-click it to open

- Add/delete/modify indicators and controls as needed

- Save the VI

- Select the desired variable