RIO Developer Essentials Guide for Academia

"FPGA personality" tag

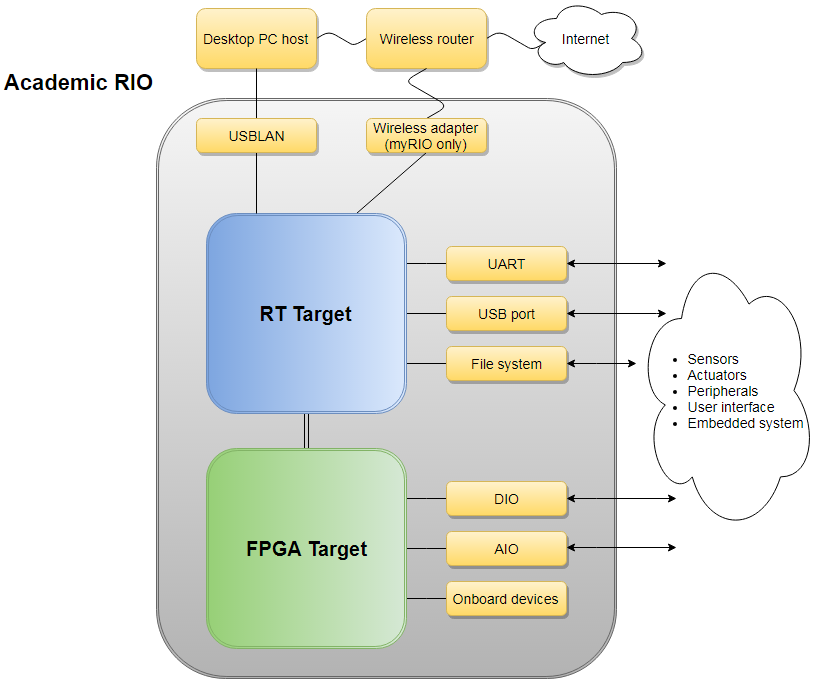

A high-level overview of the Academic RIO Device architecture and features.

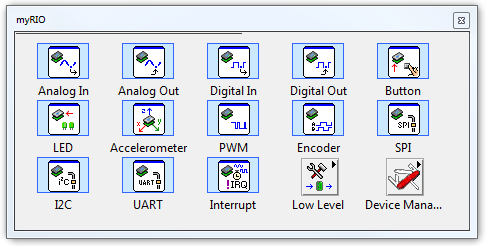

Develop Academic RIO Device applications by writing code exclusively for the RT target, and use Express VIs to access the wide variety of I/O devices implemented by the default Device FPGA personality.

Create a new LabVIEW project for the RT target, use the Academic RIO Device Toolkit and default FPGA personality, and deploy a VI as the start-up application.

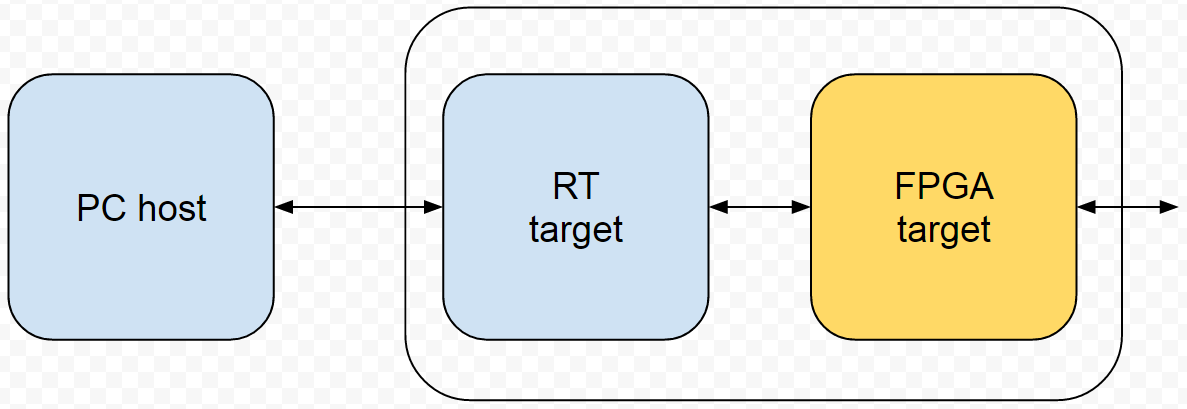

Develop an FPGA VI

FPGA guide

Develop your own FPGA-targeted VI to take advantage of the unique capabilities of the FPGA target such as high-speed I/O, precision I/O timing, parallel processing, and functionality not offered by the RT processor and Academic RIO Device Toolkit default personality; you can also augment the default personality with your needed capability.

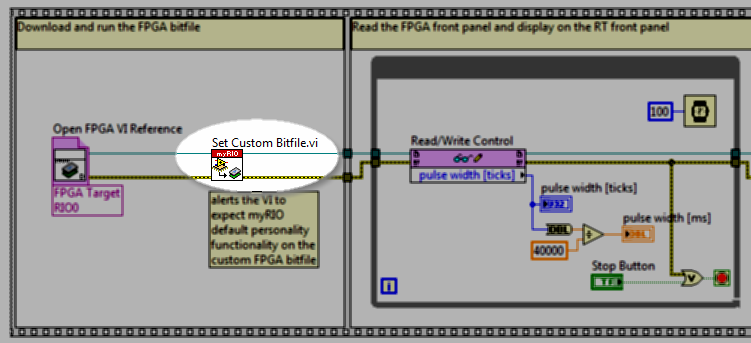

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

Load and run a modified version of the default Academic RIO Device personality (FPGA bitfile) augmented by user-defined functionality, for example, to make a high-precision measurement of pulse width.