☰

RIO Developer Essentials Guide for Academia

"Inter-target communication" tag

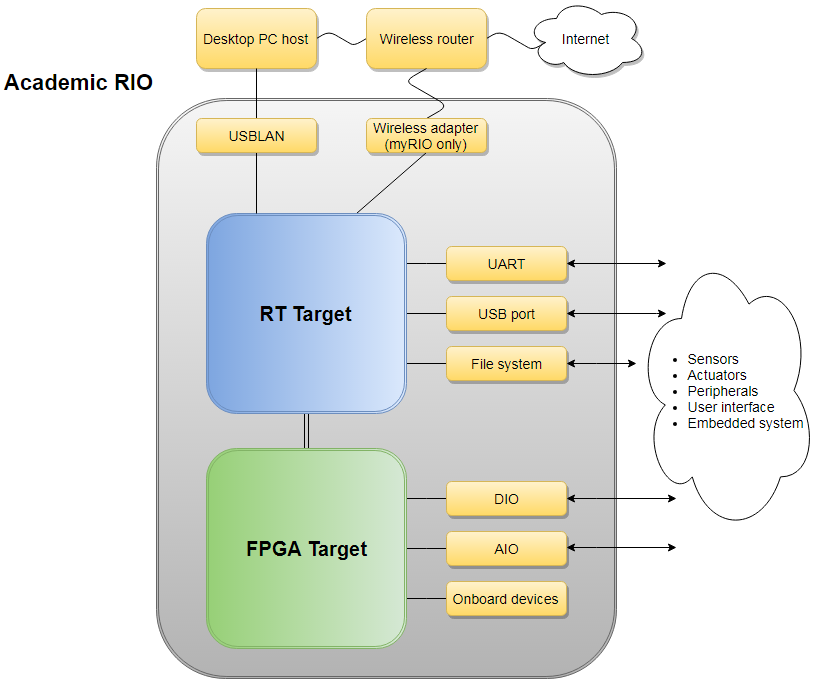

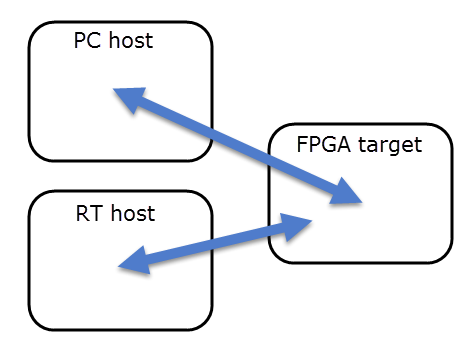

A high-level overview of the Academic RIO Device architecture and features.

Develop your own FPGA-targeted VI to take advantage of the unique capabilities of the FPGA target such as high-speed I/O, precision I/O timing, parallel processing, and functionality not offered by the RT processor and Academic RIO Device Toolkit default personality; you can also augment the default personality with your needed capability.

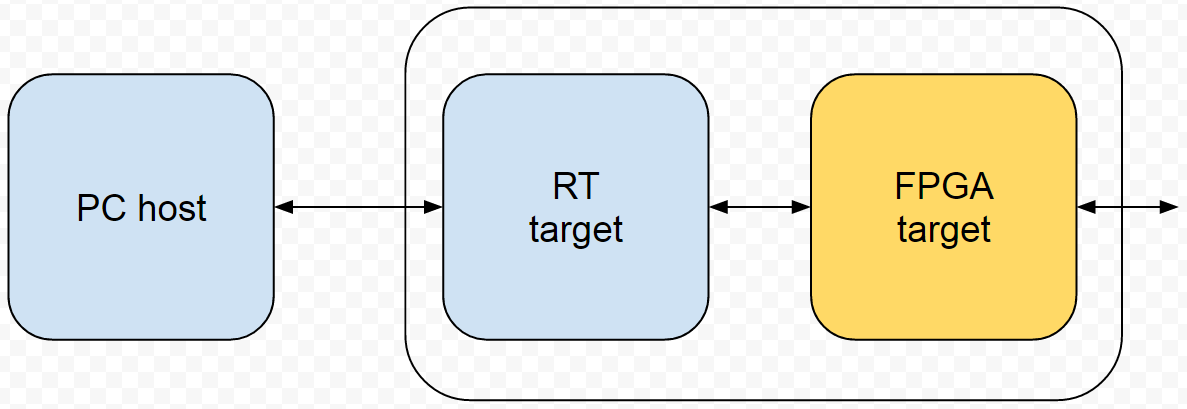

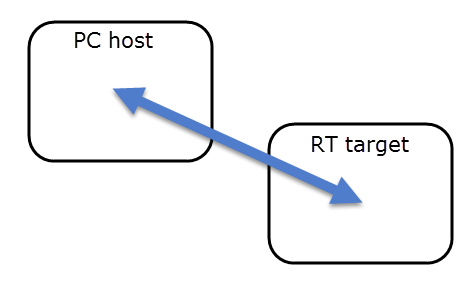

Transfer data, commands, and status between the RT target and a host system.

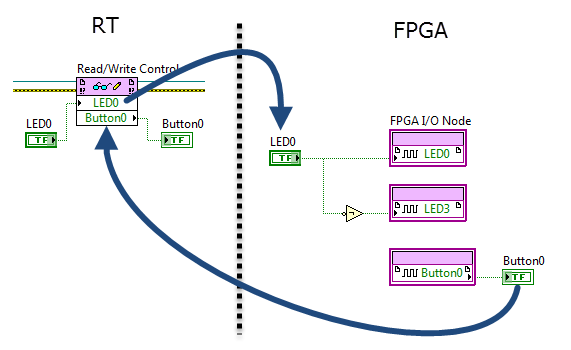

The RT VI operates (writes) the front-panel controls of the FPGA VI and reads its indicators.

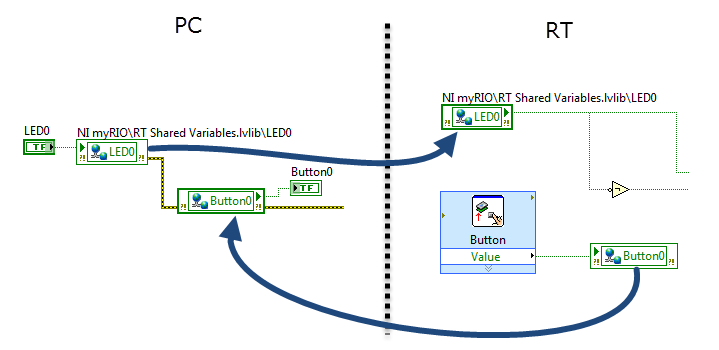

A network-published shared variable (NPSV) behaves like a global variable that links process loops residing in two or more network-connected targets.

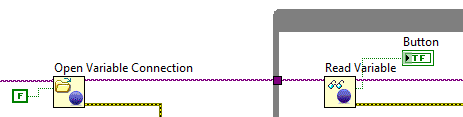

Use the NPSV programmatic API (application programmer's interface) VIs as an alternative method to a shared variable node.

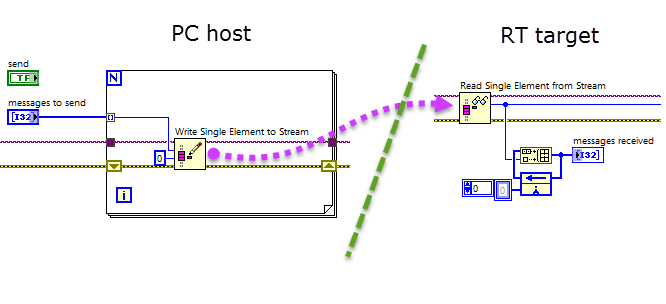

Send command and status messages through a low-latency lossless network-based data communication channel between the RT target and PC host system.

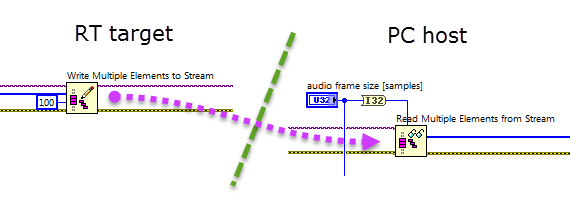

Efficiently transfer blocks of data between the RT and PC by network streams.

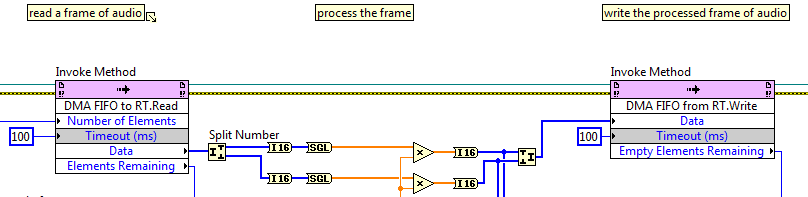

Efficiently transfer blocks of data between the RT and FPGA by direct memory access (DMA) first-in first-out (FIFO) buffers.

Transfer data, commands, and status between the FPGA target and a host system (RT or PC).

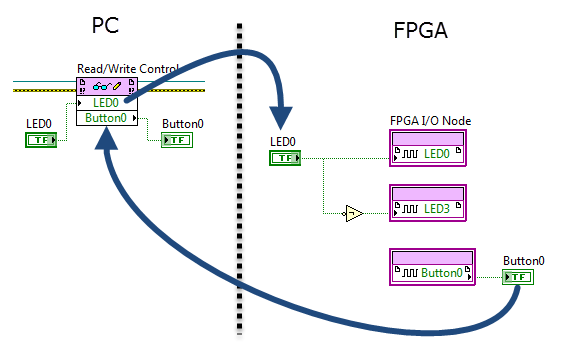

The PC VI operates (writes) the front-panel controls of the FPGA VI and reads its indicators.

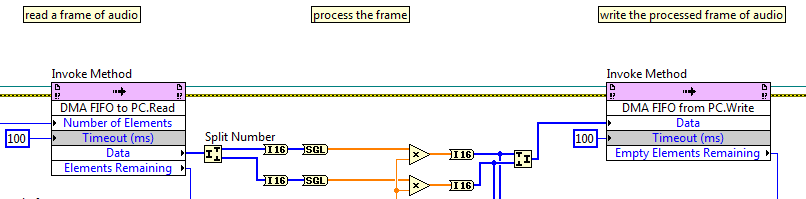

Efficiently transfer blocks of data between the PC and FPGA by direct memory access (DMA) first-in first-out (FIFO) buffers.

© 2018 National Instruments. All rights reserved.