RIO Developer Essentials Guide for Academia

"Inter-process communication" tag

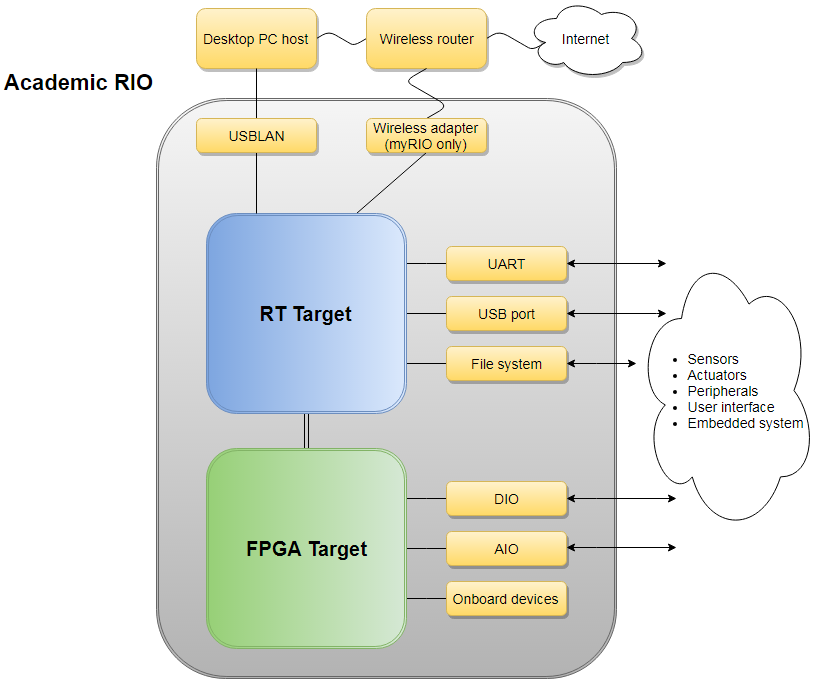

A high-level overview of the Academic RIO Device architecture and features.

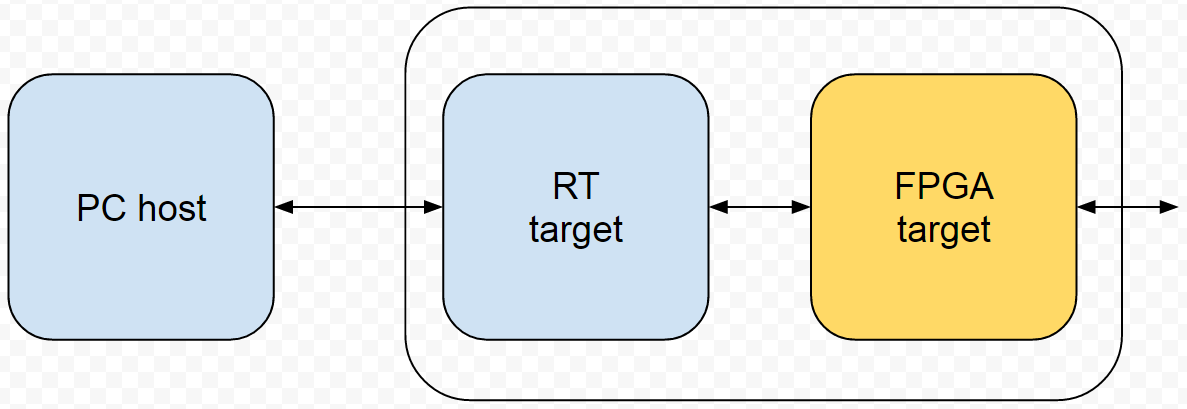

Develop an FPGA VI

FPGA guide

Develop your own FPGA-targeted VI to take advantage of the unique capabilities of the FPGA target such as high-speed I/O, precision I/O timing, parallel processing, and functionality not offered by the RT processor and Academic RIO Device Toolkit default personality; you can also augment the default personality with your needed capability.

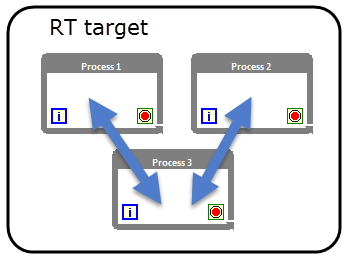

RT inter-process communication

RT guide

Exchange data between process loops running in parallel on the RT target.

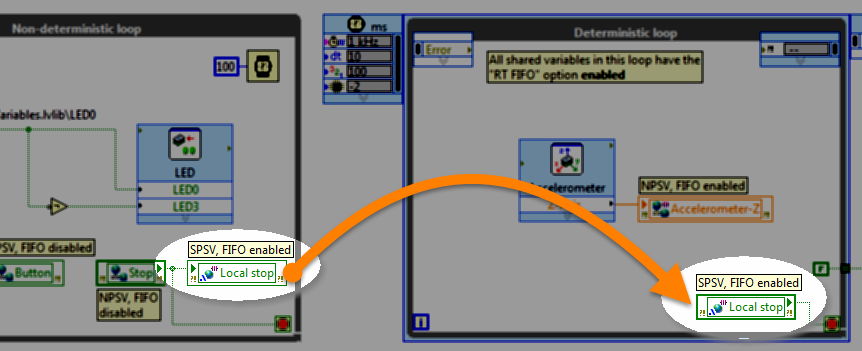

A single-process shared variable (SPSV) behaves like a global variable that links deterministic and non-deterministic process loops, effectively shielding the deterministic loop from elements that contribute jitter.

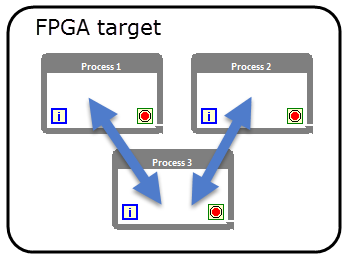

FPGA inter-process communication

RT guide

Exchange data between process loops running in parallel on the RT target.