RIO Developer Essentials Guide for Academia

RT PC code example

Stream high-speed data through a network stream channel

Efficiently transfer blocks of data between the RT and PC by network streams.

Use cases

- High throughput data transfer such as audio and signal waveforms

- Lossless data transfer, i.e., when every data point matters

Features

- Ideal for high-speed data streaming between two endpoints, one on the RT target and the other on the PC host

- Transfers any LabVIEW data type, however, best performance is achieved with numeric scalars, Booleans, and 1-D arrays of the same

- Similar to the DMA FIFO technique to stream data between the RT and FPGA and the PC and FPGA

Keep in mind

- This is streaming communication, also known as message or buffered communication

- Minimize CPU overhead per transfer by sending the largest possible block of data for each transfer

LabVIEW block diagram elements

Locate these elements with "Quick Drop" (press Ctrl+Space and start typing the name); click on an icon to see more sample code that uses that element:Example code

- Connect your Academic RIO Device to your PC using USBLAN, Ethernet, or Wi-Fi. NOTE: Not all Academic RIO Devices have Ethernet and Wi-Fi connectivity options.

-

Download and unpack the

rt-pc_network-streams-streaming.zip (for use with NI myRIO 1900)

or the

NIELVISIII-rt-pc_network-streams-streaming.zip (for use with NI ELVIS III)

archive, and then double-click the ".lvproj" file to open the project. NOTE: This project was written for a NI myRIO 1900 or NI ELVIS III connected by USBLAN at IP address 172.22.11.2.

If you are using a different IP address or another Academic RIO Device (Example: NI myRIO 1950 or NI RIO Control Module) do the following:

- If using the NI myRIO 1950 or NI RIO Control Module start with the NI myRIO 1900 Archive.

- Different IP address: Right-click on the "NI myRIO 1900" Device, choose "Properties", and then enter the new IP address

- Different device:

- Right-click on the top of the project hierarchy, select "New Targets and Devices", keep the "Existing target or device" option, and then find and select your particular device

- Select all of the components under the "NI myRIO 1900" device: click the first one and then shift+click the last one

- Drag the selected components to the new device

- Right-click the "NI myRIO 1900" device and select "Remove from project"

- Connect an audio source to the Academic RIO Device “Audio In” jack and headphones or speakers to the “Audio Out” jack

- Music from your phone is great

- This online tone generator features sine, square, sawtooth, and triangle waveforms; adjust the volume as needed

- Protect your hearing when using earbuds! Start with low volume!

- Open “RT Main” and check for a broken “Run” arrow indicating that the FPGA bitfile must be recompiled; if a recompile is necessary, expand the LabVIEW project hierarchy (Chassis >> FPGA Target >> Build Specifications), right-click on the “FPGA Main” build specification and select “Rebuild”

- Open and run “PC Main” first

- Run “RT Main”:

- The RT VI runs the supporting FPGA VI to acquire the stereo audio input waveform as audio frames (blocks of audio samples), and then sends the frames via a network stream channel to the PC for processing

- The PC VI processes the entire frame at once by applying a variable gain and then streams the frames back to the RT VI, which in turn transfers the frames to the FPGA VI for the audio output

- Front-panel controls:

- audio sampling rate: sets the FPGA sampling rate in kilo-samples per second

- audio frame size: sets the number of audio samples for each transfer

- buffer size: sets the network stream buffer size; larger values than the audio frame size are appropriate so that multiple frames may be transferred in a single transaction through the PC/RT network connection

- gain: gain factor applied to the audio: 0dB is no change, +dB boosts the level, and -dB cuts the level

- minimum loop time: increase this value to artificially extend the processing loop time to illustrate the effect of buffer overflow

- Front-panel indicators:

- depth: number of FIFO elements

- elements remaining: number of FIFO elements yet to be transferred from FPGA to PC

- overflow: FPGA upstream FIFO buffer is full and unable to accept a new audio input sample

- underflow: FPGA downstream FIFO buffer is empty and unable to produce the needed audio output sample

- maximum loop time: The maximum allowed time to keep up with the rate at which the FPGA produces and consumes audio sampled; the value in milliseconds is frame size (S/frame) divided by sampling rate (kS/s)

- measured loop time: displays the total time that the PC spends waiting for a new audio frame, processing it, and then transferring back to the FPGA

- processed audio: waveform chart display of the left (blue) and right (red) processed audio signal; right-click and choose Chart History Length to change the buffer size from default of 1024 samples

- audio sampling interval: indicates the corresponding sampling interval in microseconds according to the “audio sampling rate” control, streams the audio to the PC which applies simple processing (adjusting the gain), and then streams the processed audio back to the FPGA to be played on the audio output

- Experiment with parameters to see the effects of different frame sizes, audio sampling rates, and minimum loop time

- Increase the minimum loop time beyond the maximum allowed loop time and listen for the effects of FIFO overflow; use a sine tone to most clearly hear the noise, but you can also discern this with regular music, too.

Expected results

https://youtu.be/UQE7KCLcTBo (5:23)

Developer walk-through

NOTE: See the walk-through videos of the RT/FPGA high-speed data streaming and network-published shared variable code examples to learn about those aspects of this LabVIEW project; the following walk-through covers only the network streaming technique between the PC and RT.

https://youtu.be/WtioGKULiG8 (4:54)

Outline

- Review overall structure: “RT Main”

- Create network stream writer and reader endpoints

- “Create Network Stream Writer Endpoint” and “Create Network Stream Reader Endpoint” functions

- Name string of the form “/name”

- Datatype = U32 integers (32-bit unsigned)

- Buffer size obtained from “PC Main” via network-published shared variable (NPSV)

- Timeout = -1 causes the function to block until PC host creates the other network stream endpoint

- Main loop

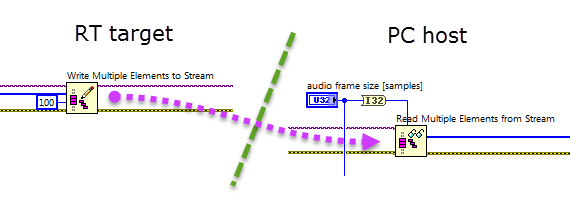

- “Write Multiple Elements to Stream” function writes the audio frame acquired from the FPGA to the PC host for processing

- “Read Multiple Elements to Stream” function reads the processed frame from the PC host and writes it the FPGA for audio output

- 100-ms timeouts prevent the functions from blocking due to inactivity on the PC host side

- PC host initiates a loop stop via a NPSV

- “Flush Stream” function ensures network stream has been read completely by PC host

- “Destroy Stream Endpoint” function closes the network stream and frees up allocated memory

- Create network stream writer and reader endpoints

- Review overall structure: “PC Main”

- Create network stream writer and reader endpoints

- Network stream URL is of the form “//IPaddress/endpoint” where “IPaddress” designates the IP address in dot-decimal notation of the RT target and “endpoint” designates the name of the RT-side reader endpoint, e.g., “RT-reader”

- “Create Network Stream Writer Endpoint” function creates the PC-side endpoint with the name “host-writer” and with buffer size and U32 data type; use 10-second timeout to block until the RT creates its corresponding endpoint

- “Create Network Stream Reader Endpoint” function creates the PC-side endpoint with the name “host-reader” and with buffer size and U32 data type; use 10-second timeout to block until the RT creates its corresponding endpoint

- The RT target is responsible for destroying these network streams when it shuts down

- Processing loop

- “Read Multiple Elements from Stream” function reads the audio frame acquired from the FPGA (via the RT) for processing

- “Write Multiple Elements to Stream” function writes the processed frame to the RT which in turn writes to the FPGA for audio output

- Create network stream writer and reader endpoints

- Locate the functions subpalette

- Network streams

For more information

- Lossless Communication with Network Streams: Components, Architecture, and Performance (http://www.ni.com/white-paper/12267/en/)

An introduction to network streams, features, and performance.

- Using the Right Networking Protocol (http://www.ni.com/white-paper/12079/en)

Discusses the three most-common communication models -- command or message-based, process data, and streaming/buffered -- and the available networking protocols that are best suited to each model: TCP, UDP, network-published shared variables, network streams, and web services.